IIC为什么绝大多数时候都是带有上拉电阻呢?

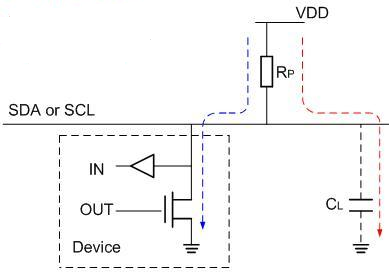

根据I2C总线规范,总线空闲时两根线都必须为高。由于I2C接口采用Open Drain机制,器件本身只能输出低电平,无法主动输出高电平,只能通过外部上拉电阻RP将信号线拉至高电平。因此I2C总线上的上拉电阻是必须的!如下图所示:

当 Master的I2C使用的是IO软件模拟时,一定要保证该两个IO上电默认均为输入(或高阻)或者输出高电平,切不可默认为输出低电平。IO默认为输入 时,可以通过外部上拉电阻将I2C信号线拉至高电平。

在单片机应用中,就要看你使用的单片机是否有标准的IIC标准接口了,如果你使用了标准的IIC接口,这个接口在使能的时候,引脚进入漏极开路模式,不过有一些单片机内 部的上拉电阻可以使能,这样就省去了外部的上拉电阻,AVR单片机,就是使能内部上拉电阻。但是如果是使用单片机的引脚模拟IIC协议,就得看你的单片机引脚是否支持漏极开路模式或者上拉模式,一般推挽模式的输出引脚用在IIC里可能会有问题。

IIC上拉电阻该如何选择?

关于这个阻值选择,以前的我一只以为是随心所欲的,但是看了一些文档,还有前辈的提醒,才了解到IIC上拉电阻也很有学问。

关于这个阻值的选取,主要牵涉到两方面,一是功耗的问题,另一个是速度的问题,二者互相矛盾的!

如果你想尽量提高速度,那么就牵涉到总线电容的问题,其实很容易理解,上拉电阻与总线的电容形成了RC,高速时将直接影响通讯!因为总线拉高时有个充电时间以及高电平的阈值,如果线上电平没有达到这个阈值时,master就以为完成了一个总线动作的话,那么通讯肯定是不能进行的!如果想尽可能降低功耗,那么就要尽可能增大电阻来减小电路各部分的消耗电流,从而实现整体降低功耗!但不可能无限大!”

IIC的上拉电阻可以是1.5K,2.2K,4.7K, 电阻的大小对时序有一定影响,对信号的上升时间和下降时间也有影响,一般接1.5K或2.2K。

I2C上拉电阻确定有一个计算公式:

Rmin={Vdd(min)-o.4V}/3mA

Rmax=(T/0.874) *c, T=1us 100KHz, T=0.3us 400KHzC是Bus capacitanceRp最大值由总线最大容限(Cbmax)决定,Rp最小值由Vio与上拉驱动电流(最大取3mA)决定;

所以Rpmin=5V/3mA≈1.7K(@Vio=5V)或者2.8V/3mA≈1K(@Vio=2.8V)

标准模式:100Kbps总线的负载最大容限<=400pF;

快速模式,400Kbps总线的负载最大容限<=200pF根据具体使用情况、 目前的器件制造工艺、PCB的走线距离等因素以及标准的向下兼容性,设计中以快速模式为基础,即总线负载电容<200pF,也就是传输速度可以上到 400Kbps是不成问题的。于是Rpmax可以取的范围是1.8K~7K @ Vio=5V对应50pF~200pF,根据Rpmin与Rpmax的限制范围,一般取5.1K @ Vio=5V , 负载容限的环境要求也容易达到。在2.8V系统中,console设计选3.3K,portable/handset等低供耗的设计选4.7K牺牲速度换取电池使用时间。

总的来说:电源电压限制了上拉电阻的最小值 ; 负载电容(总线电容)限制了上拉电阻的最大值